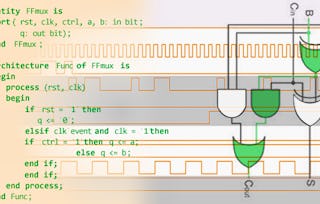

This course is designed to provide a comprehensive understanding of digital circuit design using VHDL programming with Xilinx ISE. Participants will learn the fundamentals of VHDL, simulation modeling, and design methodologies for digital circuits, including combinational and sequential circuits. Practical exercises using Xilinx ISE will enhance hands-on skills in circuit implementation, simulation, and analysis.

Design of Digital Circuits with VHDL Programming

访问权限由 Coursera Learning Team 提供

5,199 人已注册

24 条评论

推荐体验

推荐体验

中级

Professionals in FPGA Development Department, Digital System Architecture Department, and Embedded System Design Department.

24 条评论

推荐体验

推荐体验

中级

Professionals in FPGA Development Department, Digital System Architecture Department, and Embedded System Design Department.

您将获得的技能

- Application Specific Integrated Circuits

- Verification And Validation

- Electrical and Computer Engineering

- Simulation and Simulation Software

- Electronics

- Computer Engineering

- Electronic Hardware

- Hardware Design

- Development Environment

- Computational Logic

- Embedded Systems

- Electronics Engineering

- Schematic Diagrams

- Electronic Systems

- Dataflow

要了解的详细信息

添加到您的领英档案

4 项作业

了解顶级公司的员工如何掌握热门技能

积累特定领域的专业知识

- 向行业专家学习新概念

- 获得对主题或工具的基础理解

- 通过实践项目培养工作相关技能

- 获得可共享的职业证书

该课程共有4个模块

This module provides a comprehensive introduction to VHDL (VHSIC Hardware Description Language) programming, focusing on digital circuit design and simulation. Participants will learn about VHDL design elements, data objects, modeling styles, delay type modeling, operators, concurrent statements, process statements, subprograms, data flow description, behavioral description, attributes, and logic operations. The module aims to simplify VHDL programming concepts and techniques, making it accessible for beginners and providing a strong foundation for digital circuit design using VHDL.

涵盖的内容

16个视频5篇阅读材料1个作业

16个视频•总计120分钟

- About the Specialization•3分钟

- About the Course•5分钟

- Importance of VHDL Programming Language in Digital Design•10分钟

- VHDL Design and Modelling Styles - Part 1•4分钟

- VHDL Design and Modelling Styles - Part 2•10分钟

- Basic Design Elements of VHDL•8分钟

- VHDL - Object•9分钟

- Structural Description Using VHDL•10分钟

- VHDL - Configuration•10分钟

- VHDL - Operators and Process Statements•7分钟

- VHDL - Conditional Statements and Loops•10分钟

- Dataflow Description Using VHDL•6分钟

- Behavioral Description Using VHDL•8分钟

- Attributes in VHDL•8分钟

- VHDL Programming for Logic Operations - Part 1•5分钟

- VHDL Programming for Logic Operations - Part 2•6分钟

5篇阅读材料•总计50分钟

- Specialization Reading•10分钟

- Course Reading•10分钟

- Course Glossary•10分钟

- VHDL - Data Types•10分钟

- VHDL - User Defined Data Types•10分钟

1个作业•总计30分钟

- Assessment on VHDL Programming Made Easy •30分钟

This module provides a comprehensive exploration of digital combinational circuits design using VHDL programming within the Xilinx ISE Design Suite environment. Participants will delve into fundamental concepts such as AND gates, half adders, full adders, multiplexers, demultiplexers, encoders, decoders, comparators, barrel shifters, and binary-to-BCD and binary-to-Gray code converters. The module covers various VHDL modeling styles including structural, dataflow, and behavioral modeling, enabling a deep understanding of circuit design and simulation.

涵盖的内容

51个视频1个作业

51个视频•总计455分钟

- Xilinx ISE Installation and its Design Flow - Part 1•8分钟

- Xilinx ISE Installation and its Design Flow - Part 2•7分钟

- Xilinx ISE Installation and its Design Flow - Part 3•11分钟

- Structural Modelling Style in VHDL with Half Adder - Part 1•9分钟

- Structural Modelling Style in VHDL with Half Adder - Part 2•8分钟

- Structural Modelling Style in VHDL with Half Adder - Part 3•8分钟

- Structural Modelling Style in VHDL with Half Adder - Part 4•8分钟

- Dataflow Modelling Style in VHDL with Half Adder - Part 1•9分钟

- Dataflow Modelling Style in VHDL with Half Adder - Part 2•8分钟

- Behavioral Modelling Style in VHDL with Half Adder - Part 1•10分钟

- Behavioral Modelling Style in VHDL with Half Adder - Part 2•8分钟

- Design of Full Adder Using Various Modelling Styles in VHDL - Part 1•14分钟

- Design of Full Adder Using Various Modelling Styles in VHDL - Part 2•10分钟

- Design of Full Adder Using Various Modelling Styles in VHDL - Part 3•7分钟

- Design of Full Adder Using Various Modelling Styles in VHDL - Part 4•8分钟

- Design of Full Adder Using Various Modelling Styles in VHDL - Part 5•8分钟

- Design of Full Adder Using Various Modelling Styles in VHDL - Part 6•7分钟

- Design of Full Adder Using Various Modelling Styles in VHDL - Part 7•11分钟

- Design of 4-bit Ripple Carry Adder (RCA) Using Various Modelling Styles in VHDL - Part 1•13分钟

- Design of 4-bit Ripple Carry Adder (RCA) Using Various Modelling Styles in VHDL - Part 2•9分钟

- Design of 4-bit Ripple Carry Adder (RCA) Using Various Modelling Styles in VHDL - Part 3•9分钟

- Design of 4-bit Ripple Carry Adder (RCA) Using Various Modelling Styles in VHDL - Part 4•6分钟

- Design of 4-bit Ripple Carry Adder (RCA) Using Various Modelling Styles in VHDL - Part 5•8分钟

- Design of 4-bit Ripple Carry Adder (RCA) Using Various Modelling Styles in VHDL - Part 6•7分钟

- Design of Multiplexer Using Various Modelling Styles in VHDL - Part 1•10分钟

- Design of Multiplexer Using Various Modelling Styles in VHDL - Part 2•10分钟

- Design of Multiplexer Using Various Modelling Styles in VHDL - Part 3•12分钟

- Design of Multiplexer Using Various Modelling Styles in VHDL - Part 4•8分钟

- Design of Multiplexer Using Various Modelling Styles in VHDL - Part 5•8分钟

- Design of Demultiplexer Using Various Modelling Styles in VHDL - Part 1•12分钟

- Design of Demultiplexer Using Various Modelling Styles in VHDL - Part 2•6分钟

- Design of Demultiplexer Using Various Modelling Styles in VHDL - Part 3•11分钟

- Design of Demultiplexer Using Various Modelling Styles in VHDL - Part 4•12分钟

- Design of Encoder Using Various Modelling Styles in VHDL - Part 1•9分钟

- Design of Encoder Using Various Modelling Styles in VHDL - Part 2•5分钟

- Design of Encoder Using Various Modelling Styles in VHDL - Part 3•9分钟

- Design of Encoder Using Various Modelling Styles in VHDL - Part 4•12分钟

- Design of Decoder Using Various Modelling Styles in VHDL - Part 1•12分钟

- Design of Decoder Using Various Modelling Styles in VHDL - Part 2•5分钟

- Design of Decoder Using Various Modelling Styles in VHDL - Part 3•10分钟

- Design of Decoder Using Various Modelling Styles in VHDL - Part 4•11分钟

- Design of 4-bit Comparator Using Various Modelling Styles in VHDL - Part 1•10分钟

- Design of 4-bit Comparator Using Various Modelling Styles in VHDL - Part 2•10分钟

- Design of 4-bit Comparator Using Various Modelling Styles in VHDL - Part 3•8分钟

- Design of 4-bit Comparator Using Various Modelling Styles in VHDL - Part 4•9分钟

- Design of 8-bit Barrel Shifter Using VHDL - Part 1•12分钟

- Design of 8-bit Barrel Shifter Using VHDL - Part 2•7分钟

- Design of 4-bit Binary to BCD Converter in VHDL - Part 1•8分钟

- Design of 4-bit Binary to BCD Converter in VHDL - Part 2•5分钟

- Design of 4-bit Binary to Grey Code Converter in VHDL - Part 1•7分钟

- Design of 4-bit Binary to Grey Code Converter in VHDL - Part 2•6分钟

1个作业•总计30分钟

- Assessment on Design of Digital Combinational Circuits with VHDL Programming Using Xilinx ISE•30分钟

This module focuses on the design and implementation of digital sequential circuits using VHDL programming within the Xilinx ISE-I environment. Participants will delve into fundamental sequential circuit components such as D latch, D flip-flop, SR flip-flop, JK flip-flop, T flip-flop, shift registers, counters, and FIFO memories. Various VHDL modeling styles including structural, dataflow, and behavioral modeling will be utilized to develop and analyze the functionality of these sequential circuits.

涵盖的内容

20个视频1个作业

20个视频•总计173分钟

- Design of D Latch Using Various Modelling Styles in VHDL - Part 1•10分钟

- Design of D Latch Using Various Modelling Styles in VHDL - Part 2•6分钟

- Design of D Latch Using Various Modelling Styles in VHDL - Part 3•10分钟

- Design of D Latch Using Various Modelling Styles in VHDL - Part 4•11分钟

- Design of D Flip Flop using VHDL•13分钟

- Design of SR Flip Flop using VHDL - Part 1•8分钟

- Design of SR Flip Flop using VHDL - Part 2•7分钟

- Design of JK Flip Flop using VHDL - Part 1•7分钟

- Design of JK Flip Flop using VHDL - Part 2•9分钟

- Design of T Flip Flop using VHDL•11分钟

- Design of 5-bit Shift Register Using VHDL Part 1•12分钟

- Design of 5-bit Shift Register Using VHDL Part 2•6分钟

- Design of Universal Shift Register using VHDL - Part 1•10分钟

- Design of Universal Shift Register Using VHDL - Part 2•9分钟

- Design of 4-bit Counter Using VHDL - Part 1•7分钟

- Design of 4-bit Counter Using VHDL - Part 2•6分钟

- Design of First in First Out (FIFO) Memory Using VHDL Part 1•7分钟

- Design of First in First Out (FIFO) Memory Using VHDL Part 2•6分钟

- Design of Asynchronous First in First Out (FIFO) Memory Using VHDL Part 1•11分钟

- Design of Asynchronous First in First Out (FIFO) Memory Using VHDL Part 2•6分钟

1个作业•总计30分钟

- Assessment on Design of Digital Sequential Circuits with VHDL Programming Using Xilinx ISE-I•30分钟

This module delves into the design and implementation of digital sequential circuits using VHDL programming techniques within the Xilinx ISE-II environment. Participants will explore various sequential circuit components such as Single Port RAM, Dual Port RAM, sequence detectors (including Mealy and Moore machines), and a digital model of a vending machine. The module emphasizes hands-on learning, combining theoretical concepts with practical design and simulation exercises to develop a comprehensive understanding of digital sequential circuit design methodologies.

涵盖的内容

23个视频1个作业

23个视频•总计182分钟

- Design of Single Port RAM using VHDL - Part 1•7分钟

- Design of Single Port RAM using VHDL - Part 2•8分钟

- Design of Dual Port RAM using VHDL - Part 1•7分钟

- Design of Dual Port RAM using VHDL - Part 2•9分钟

- Design of Mealy Non-overlapping 3-bit Sequence Detector using VHDL - Part 1•7分钟

- Design of Mealy Non-overlapping 3-bit Sequence Detector using VHDL - Part 2•7分钟

- Design of Mealy Non-overlapping 3-bit Sequence Detector using VHDL - Part 3•6分钟

- Design of Mealy Non-overlapping 5-bit Sequence Detector using VHDL - Part 1•11分钟

- Design of Mealy Non-overlapping 5-bit Sequence Detector using VHDL - Part 2•6分钟

- Design of Mealy Overlapping 3-bit Sequence Detector using VHDL - Part 1•9分钟

- Design of Mealy Overlapping 3-bit Sequence Detector using VHDL - Part 2•7分钟

- Design of Mealy Overlapping 5-bit Sequence Detector Using VHDL Part 1•10分钟

- Design of Mealy Overlapping 5-bit Sequence Detector Using VHDL Part 2•7分钟

- Design of Moore Non-overlapping 3-bit Sequence Detector Using VHDL Part 1•12分钟

- Design of Moore Non-overlapping 3-bit Sequence Detector Using VHDL Part 2•6分钟

- Design of Moore Non-overlapping 5-bit Sequence Detector using VHDL - Part 1•10分钟

- Design of Moore Non-overlapping 5-bit Sequence Detector using VHDL - Part 2•6分钟

- Design of Moore Overlapping 3-bit Sequence Detector Using VHDL Part 1•10分钟

- Design of Moore Overlapping 3-bit Sequence Detector Using VHDL Part 2•6分钟

- Design of Moore Overlapping 5-bit Sequence Detector using VHDL - Part 1 •9分钟

- Design of Moore Overlapping 5-bit Sequence Detector using VHDL - Part 2•6分钟

- Design of Vending Machine Using VHDL Part 1•8分钟

- Design of Vending Machine Using VHDL Part 2•10分钟

1个作业•总计30分钟

- Assessment on Design of Digital Sequential Circuits with VHDL Programming Using Xilinx ISE-II•30分钟

获得职业证书

将此证书添加到您的 LinkedIn 个人资料、简历或履历中。在社交媒体和绩效考核中分享。

位教师

授课教师评分

我们要求所有学生根据授课教师的教学风格和质量提供对授课教师的反馈。

提供方

提供方

Larsen & Toubro popularly known as L&T is an Indian Multinational conglomerate. L&T has over 8 decades of expertise in executing some of the most complex projects including the World's tallest statue - the Statue of Unity. L&T has a wide portfolio that includes engineering, construction, manufacturing, realty, ship building, defense, aerospace, IT & financial services. L&T EduTech is a e learning platform within the L&T Group, that offers courses that are curated & delivered by industry experts. In the world of engineering and technology, change and advancements are happening at the speed of light. Academia needs to keep pace with this change and career professionals need to adapt. This is the need gap L&T EduTech will fill. The vision for L&T EduTech is to be the bridge between academia and industry, between career professionals and ever-changing technology. L&T EduTech firmly believes that, only when these need gaps are filled, will we have truly empowered and knowledgeable workforce that will lead India in the future.

人们为什么选择 Coursera 来帮助自己实现职业发展

Felipe M.

Jennifer J.

Larry W.

Chaitanya A.

学生评论

24 条评论

- 5 stars

75%

- 4 stars

8.33%

- 3 stars

0%

- 2 stars

8.33%

- 1 star

8.33%

显示 3/24 个

已于 Jun 11, 2025审阅

This course is amazing to start the VLSI Domain journey.

从 Physical Science and Engineering 浏览更多内容

课程

专项课程

U

UUniversitat Autònoma de Barcelona

课程